- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-SDRAM/DDR2 (Altera)IP DDR2 SDRAM CONTROLLER

�� �

�

�

�2–22�

�Chapter� 2:� Getting� Started�

�MegaWizard� Plug-In� Manager� Design� Flow�

�2.� Launch� your� simulation� tool� inside� this� directory� and� create� the� following�

�libraries:�

�■�

�■�

�<� device� name� >� _ver�

�auk_ddr_user_lib�

�3.� Compile� the� files� in� Table� 2–5� into� the� appropriate� library.�

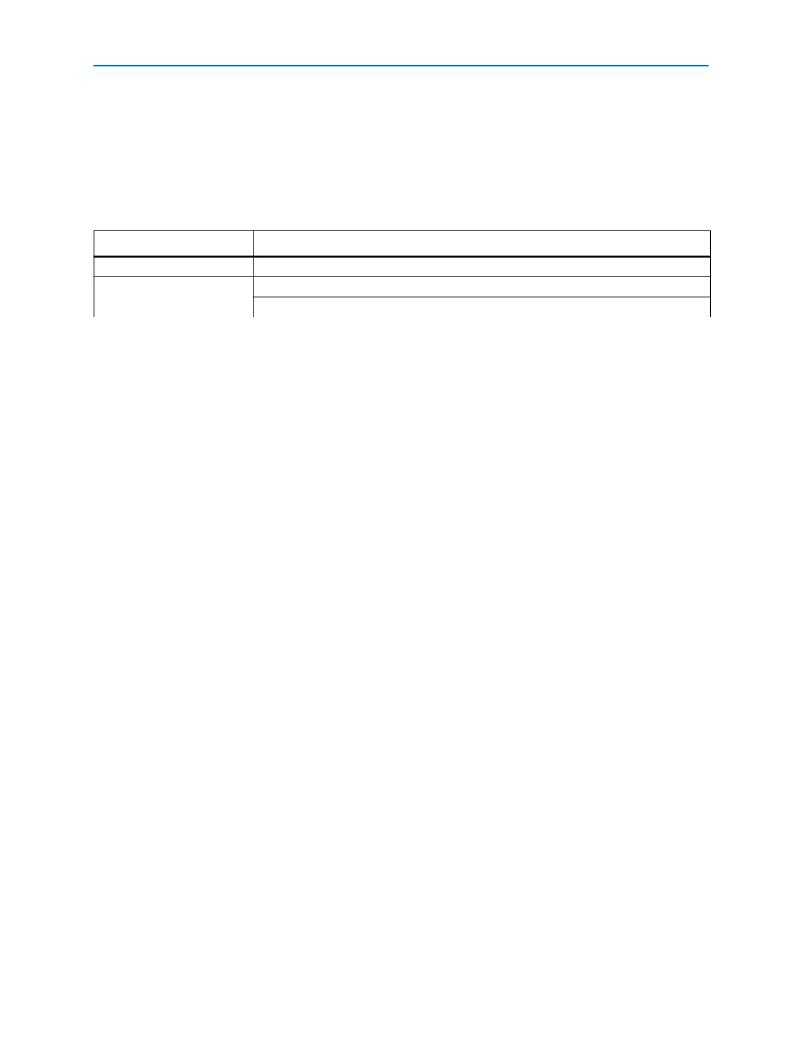

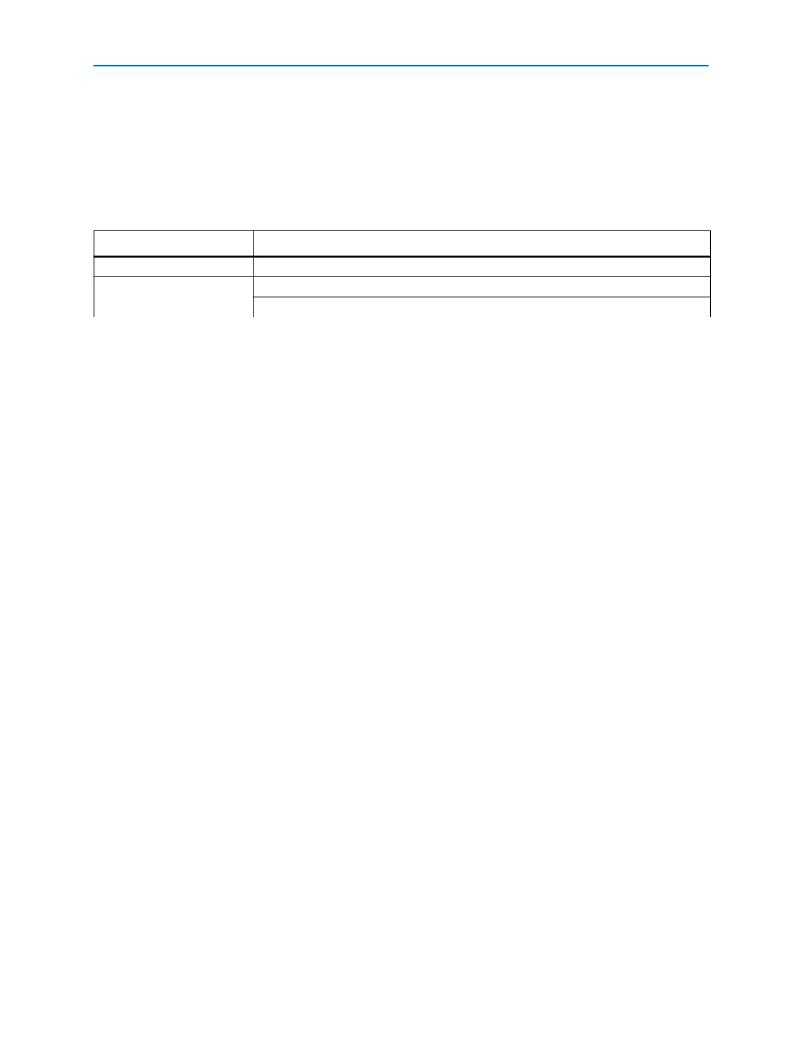

�Table� 2–5.� Files� to� Compile—Verilog� HDL� Gate-Level� Simulations�

�Library�

�<� device� name� >� _ver�

�auk_ddr_user_lib�

�Filename�

�<� QUARTUS� ROOTDIR� >� /eda/sim_lib/� <� device� name� >� _atoms.v�

�<� project� directory� >� /testbench/simulation/� <� simulator� name� >� /<toplevel_name>.vo� (1)�

�<� project� directory� >� /testbench/� <� testbench� name� >� .v�

��(1)� If� you� are� simulating� the� slow� or� fast� model.,� the� .vho� file� has� a� suffix� _min� or� _max� added� to� it.� Compile� whichever� file� is� appropriate.� The�

�Quartus� II� software� creates� models� for� the� simulator� you� have� defined� in� a� directory� simulation/� <� simulator� name� >� in� your� <� project� name� >�

�directory..�

�4.� Set� the� Tcl� variable� gRTL_DELAYS� to� 0,� which� tells� the� testbench� not� to� use� the�

�insert� extra� delays� in� the� system,� because� these� are� applied� inside� the� gate� level�

�model.� Configure� your� simulator� to� use� transport� delays,� a� timestep� of�

�picoseconds,� and� to� include� the� <� device� name� >� _ver� library.�

�Compile� the� Example� Design�

�You� can� now� edit� the� PLL(s)� and� use� the� Quartus� II� software� to� compile� the� example�

�design� and� perform� post-compilation� timing� analysis.�

�Edit� the� PLL�

�The� IP� Toolbench-generated� example� design� includes� a� PLL,� which� has� an� input� to�

�output� clock� ratio� of� 1:1� and� a� clock� frequency� that� you� entered� in� IP� Toolbench.� In�

�addition,� IP� Toolbench� correctly� sets� all� the� phase� offsets� of� all� the� relevant� clock�

�outputs� for� your� design.� You� can� edit� the� PLL� input� clock� to� make� it� conform� to� your�

�system� requirements.� If� you� re-run� IP� Toolbench,� it� does� not� overwrite� this� PLL,� if�

�you� turn� off� Automatically� generate� the� PLL� ,� so� your� edits� are� not� lost.�

�1�

�1�

�f�

�If� you� turn� on� Use� fed-back� clock� ,� IP� Toolbench� generates� a� second� PLL—the� fed-back�

�PLL.� You� need� not� edit� the� fed-back� PLL.�

�If� you� change� the� clock� input� frequency� on� the� PLL,� you� must� change� the�

�REF_CLOCK_TICK_IN_PS� parameter� in� the� <� project� name� >� _tb.v� or� .vhd� file.�

��To� edit� the� example� PLL,� follow� these� steps:�

�1.� Choose� MegaWizard� Plug-In� Manager� (Tools� menu).�

�2.� Select� Edit� an� existing� custom� megafunction� variation� and� click� Next� .�

�3.� In� your� Quartus� II� project� directory,� for� VHDL� choose� ddr_pll_� <device� name>� .vhd� ;�

�for� Verilog� HDL� choose� ddr_pll_� <device� name>� .v� .�

��?� March� 2009� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-SLITE2

IP SERIALLITE II

IP-SRAM/QDRII

IP QDRII SRAM CONTROLLER

IP-VITERBI/SS

IP VITERBI LOW-SPEED

IP4220CZ6,125

IC USB DUAL ESD PROTECT 6TSOP

IPA-66-1-600-10.0-A-01-T

CIRC BRKR 10A 2POLE SCREW TERM

IPR-CSC

IP COLOR SPACE CONVERTER RENEW

IPR-ED8B10B

IP 8B10B ENCODER/DECODER RENEW

IPS-VIDEO

IP VIDEO/IMAGE PROCESSING SUITE

相关代理商/技术参数

IP-SDRAM/DDR3

功能描述:开发软件 DDR3 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR

功能描述:开发软件 DDR SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/HPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IP-SDRAM/LPDDR2

功能描述:开发软件 DDR2 SDRAM Control MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPSE.4.33SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.33SM600 GLASS FIBER (MIN ORDER 50)

IPSE.4.62SM600

制造商:Banner Engineering 功能描述:FIBER IPSE.4.62SM600 GLASS FIBER (MIN ORDER 50)

IPS-EMBEDDED

功能描述:开发软件 Embedded IP Suite MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPS-EVAL-EH-01

功能描述:ENERGY HARVESTING BOARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:THINERGY® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP